Our Product

- High Speed Digital Logic

- Clock Drivers & Low-skew Clock Buffers

- Phase Lock Loop and VCO

- Phase Lock Loop and VCO

- Industrial Analog Devices

- Audio, Video & Telecom ICs

Engineering

Project Feasibility Study

- Data Sheet & Product Functionality Review and Analysis

- Determination of Required Tests based on Product application and Electrical parameter specifications

- Tabulation of Test methodology for each test with input / output conditions & limits, in the form of a Test Plan Matrix

- Agreement with Customer on the derived Test Plan Matrix & Scope finalization

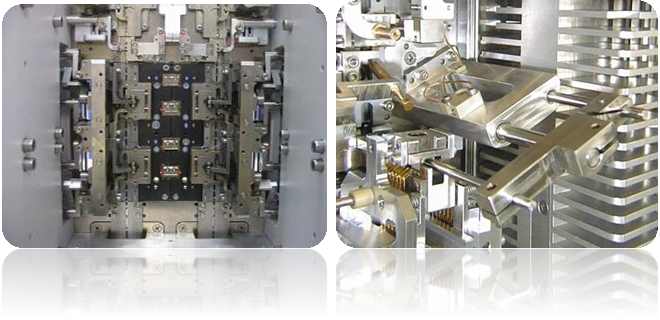

Hardware Design & Fabrication

- Selection of appropriate Tester platform capable of handling the product for the agreed Test Plan Matrix

- Design of the product hardware load board schematic and the Adaptor Board for interfacing with the DUT.

- Selection of Manual Test Socket, Handler Contractor Mechanism inclusive of the Mechanical interface design

- Design of the probe card based on the die pad layout and suitable interface with the Tester Load Board.

- Fabrication of designed hardware modules like Load Board, Manual DUT Board, Handler Interface Board & the Probe Cards

Program Development & Debugging

- Development of the test program code for the designed hardware schematic as per the agreed Test Plan Matrix conditions.

- Debugging of the program using the constructed hardware modules and known good products

- Verification of test measurement data for each parameter

- Refinement of hardware or test program depending upon the product characteristics & the observed values, for better performance

- Test Time Optimization is considered as part of the program debugging

Product Characterization & Correlation

- Verification & Refinement of the developed application program and set-up using Correlation Units provided by the Customer, wherever available.

- Correlation of Tester measurements with Bench parameter values in case of non-availability of known correlation units

- Electrical Characterization of New products for various parameters & input conditions.

- Statistical Analysis of the measured values & Determination of test limits

- Generation of Schmoo & Statistical distribution plots wherever possible for review by the Design team

Production

General

- Capabilities to test products in both packaged level component form as well as die level wafer form.

- Assignment of Unique Traceable Production Lot Numbers and Tracking of individual Lot test data

- On-line Monitoring of Test Yields and Analysis / Reporting of Low Yielding Engineering Lots.

- Even load balancing technique is adopted to handle any sudden spike in the production volumes, than the usuals.

- Fool-proof reject handling mechanism at all stages of Testing.

- Controlled Test Program Release & Revision Control

- Controlled Load Boards & associated Hardware Maintenance

- Documented well established set-up verification procedures

Component Test

- Single-site & Multi-Site handling capabilities

- Kelvin and True Plunge to Board Contacts available

- Soft and Hard Docking Handler Mechanisms

- In-house design & fabrication of Handler Contractor Interface

- On-line inspection of Visual Mechanical Parameters

Wafer Test

- Single-site & Multi-Site handling capabilities

- Offline and Online Inking capabilities

- Wafer Sort Results available in Standard Map formats

- On-line inspection of Probe & Ink Mark